隨著摩爾定律演進放緩與異構集成、Chiplet(芯粒)等技術的興起,集成電路產業正步入一個全新的融合時代。設計復雜度呈指數級增長,異構系統集成了數字、模擬、射頻、存儲乃至光電子等不同工藝、不同功能的模塊,這對傳統的集成電路設計流程,特別是測試環節,提出了前所未有的挑戰。在這一背景下,打造穩定、高效、智能的自動測試設備(ATE)不僅是保障產品質量與可靠性的基石,更是抓住融合時代機遇、搶占技術制高點的關鍵。

一、 融合時代的測試新挑戰

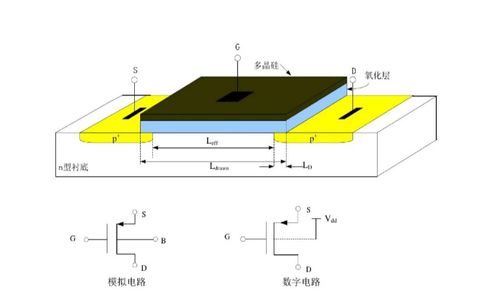

- 設計復雜度與異構性激增:現代SoC(片上系統)集成了數十億甚至上百億晶體管,并融合了多種計算單元、加速器和專用IP。測試向量生成、故障覆蓋率評估的難度極大提升。混合信號、高速接口(如DDR5/PCIe 6.0)的測試要求精度與時序控制達到前所未有的水平。

- 測試成本與時間壓力:測試成本在芯片總成本中的占比日益升高。復雜的測試程序、漫長的測試時間與高昂的ATE設備投資形成了巨大矛盾。如何在保證測試質量的顯著壓縮測試時間、降低單顆芯片測試成本,成為產業核心痛點。

- 可靠性要求與生命周期管理:在汽車電子、工業控制、數據中心等關鍵領域,芯片的可靠性與長期穩定性至關重要。測試不再局限于出廠前的功能驗證,還需覆蓋老化測試、在線監控、失效分析等全生命周期質量保障。

- 數據洪流與智能分析需求:測試過程中產生的海量數據(電參數、時序、溫度、良率等)蘊含豐富信息。如何實時采集、高效管理并利用人工智能/機器學習技術進行深度分析,實現預測性維護、測試程序優化和良率提升,是智能化測試的核心。

二、 多維度打造穩定高效的ATE系統

應對上述挑戰,需要從硬件、軟件、方法學和生態系統多個維度進行系統性創新與協同。

1. 硬件平臺:向高精度、高靈活性與高密度演進

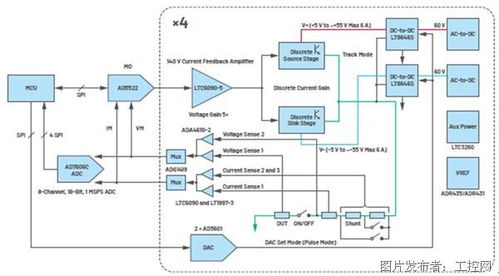

模塊化與可擴展架構:采用高度模塊化的硬件平臺,支持數字、模擬、射頻、大功率等不同測試資源的靈活配置與平滑升級,以快速適應不同芯片(尤其是Chiplet)的測試需求。

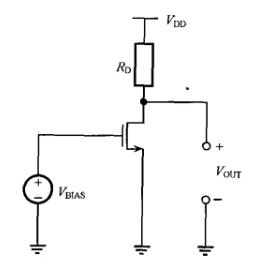

高性能引腳電子與儀器:提升引腳電子的數據速率、時序精度和電壓/電流測量范圍,滿足高速SerDes、高精度數據轉換器(ADC/DAC)等接口的嚴苛測試要求。

并行測試與多站點能力:通過增強數字通道密度、優化資源共享架構,大幅提升并行測試能力(同測數),有效攤薄測試成本。需解決多站點測試下的功耗、散熱與信號完整性問題。

集成化與靠近DUT(被測器件):將部分測試功能(如電源管理、簡單激勵/響應)集成到負載板(Load Board)或探針卡(Probe Card)上,縮短信號路徑,提高測試速度與信號保真度。

2. 軟件與算法:智能、開放與自動化

智能測試程序生成(TPG):利用AI算法,基于設計仿真數據、歷史測試數據自動生成和優化測試向量,在保證故障覆蓋率的前提下,大幅壓縮測試模式長度。

自適應測試與實時優化:在測試過程中實時分析芯片性能參數,動態調整測試條件(如電壓、頻率),實現芯片性能分級(Bin Split)或篩選潛在早期失效器件,提升整體產品品質與價值。

開放統一的軟件框架:提供標準化API和開發環境,方便用戶集成第三方工具、自定義算法和數據分析流程,形成從設計仿真、測試開發到生產數據分析的完整工具鏈。

大數據分析與良率管理系統:構建集成的數據分析平臺,將ATE數據與晶圓制造(WAT/CP)、封裝(FT)乃至系統級測試(SLT)數據關聯分析,快速定位缺陷根因,驅動設計與工藝改進。

3. 測試方法學創新

基于DFT(可測試性設計)的協同:推動測試工程師與設計工程師的早期協作,采用先進的DFT技術,如IEEE 1687(IJTAG)、內建自測試(BIST)、掃描壓縮等,簡化ATE測試復雜度,提升測試效率。

系統級測試(SLT)與ATE的融合:針對復雜SoC和異構集成芯片,將部分應用場景下的功能測試(SLT)與ATE的結構化測試相結合,形成互補的測試策略,在成本與覆蓋率之間取得最佳平衡。

* 面向Chiplet與先進封裝的測試策略:發展KGD(已知合格芯片)測試、中間測試(Interposer/Bridge測試)和最終系統級測試的分層測試方案,確保每個Chiplet和集成后的系統均滿足性能與可靠性要求。

4. 構建協同生態系統

產業上下游深度合作:ATE供應商需與EDA工具商、IP提供商、晶圓代工廠、封裝測試廠乃至終端系統廠商建立更緊密的伙伴關系,共同定義測試標準,開發聯合解決方案。

人才培養與知識共享:培養兼具集成電路設計、測試理論和數據分析能力的復合型人才。通過行業論壇、技術聯盟促進知識交流與最佳實踐分享。

三、 擁抱機遇,引領未來

集成電路的融合時代,既是挑戰的匯聚點,也是創新的催化劑。自動測試設備作為連接設計與制造的“質量守門人”,其角色正從被動驗證向主動賦能轉變。通過從硬件性能、軟件智能、方法學創新到生態協同的多維度入手,打造下一代穩定、高效、智能的ATE系統,我們不僅能有效應對當前復雜芯片的測試難題,更能為即將到來的、由異構集成和Chiplet技術驅動的產業新浪潮奠定堅實基礎。唯有如此,整個集成電路產業才能在融合時代的機遇與挑戰中行穩致遠,持續引領信息技術的革命性進步。